Vias sont l‘un des éléments importants de PCB multicouches. Le coût du forage représente habituellement 30% à 40% des coûts de fabrication de circuits imprimés. Autrement dit, peut être appelé chaque trou sur la carte électronique via un.

Tout d‘abord:parasiteCapacitance deVia

La via lui-même a une capacité parasite à la masse. Si le diamètre du trou d‘isolement de l‘intermédiaire sur la couche de sol est connu pour être D2, le diamètre du plot de traversée est D1, et l‘épaisseur de la carte de circuit imprimé est T, et le substrat constant de la carte diélectrique estε, La capacité parasite du trou d‘interconnexion est d‘environ: C=1,41εTD1 / (D2-D1).

Le principal effet de la capacité parasite du circuit par l‘intermédiaire de l‘est de prolonger le temps de montée du signal et de réduire la vitesse du circuit. Par exemple, pour un circuit imprimé avec une épaisseur de 50 mil, si un trou avec un diamètre intérieur de 10 mil et un diamètre de tampon de 20 mil est utilisé, et la distance entre le patin et la surface de cuivre de masse est 32Mil, alors on peut se rapprocher de la via par la formule ci-dessus: la capacité parasite est d‘environ:

C=1.41x4.4x0.050x0.020 / (0,032 à 0,020)=0.517pF.

La variation du temps de montée provoquées par cette partie du condensateur est: T10-90=2.2C (Z0 / 2)=2.2x0.517x (55 / 2)=31.28ps.

A partir de ces valeurs, on peut voir que même si l‘effet de ralentir le retard de montée causée par la capacité parasite d‘un seul via est pas très évident. Toutefois, si vias sont utilisés plusieurs fois pour basculer entre les couches, les concepteurs doivent encore examiner attentivement.

deuxième:TilParasiticJenductance duVia

De même, la capacité parasite et l‘inductance existent dans la via. Dans la conception des circuits numériques à grande vitesse, les dommages causés par l‘inductance parasite du trou est généralement supérieur à l‘effet de la capacité parasite. Son inductance série parasite affaiblit le rôle des condensateurs de dérivation et d‘affaiblir l‘effet de filtrage de l‘ensemble du système d‘alimentation. Nous pouvons utiliser la formule suivante pour calculer simplement l‘inductance parasite approximative de la via: L=5.08h [ln (4 h / j) + 1]. Où L est l‘inductance de la via, h est la longueur du trou d‘interconnexion, et d est le diamètre du centre. On peut voir à partir de la formule que le diamètre du trou d‘interconnexion a peu d‘effet sur l‘inductance, tandis que la longueur de la via a la plus grande influence sur l‘inductance. Toujours à l‘aide de l‘exemple ci-dessus, l‘inductance de la via peut être calculée comme suit: L=5.08x0.050 [ln (4x0.050 / 0,010) +1]=1.015nH. Si le temps de montée du signal est de 1 ns, l‘impédance équivalente est: XL=πL / T10-90=3.19Ω. Ce type d‘inductance ne peut plus être ignoré lors du passage des courants de fréquence élevée. Il est important de noter que les besoins de condensateur d‘insertion à passer à travers deux trous d‘interconnexion pour connecter la couche d‘alimentation et la couche de masse, de sorte que l‘inductance parasite des vias vont se multiplier.

Troisième:Via la conception de PCB à haute vitesse

Grâce à l‘analyse ci-dessus des caractéristiques parasites des vias, nous pouvons voir que dans la conception de PCB à haute vitesse, les vias simples en apparence généralement apporter aussi un grand impact négatif sur la conception du circuit. Afin de réduire les effets négatifs causés par les effets parasites des vias, dans la conception, vous pouvez le faire autant que possible:

1. Compte tenu de la qualité des coûts et du signal, s‘il vous plaît choisir un par de taille raisonnable. Par exemple, pour la conception de la mémoire 6-10 couche module PCB, il est préférable d‘utiliser 10/20 mil (perçage / pad) vias. Pour certains conseils de petite taille haute densité, vous pouvez aussi utiliser le trou 8 / 18Mil. Dans les conditions techniques actuelles, il est difficile d‘utiliser par des trous d‘une taille plus petite. Pour vias pour le pouvoir ou le sol, utilisez des tailles plus grandes pour réduire l‘impédance.

2. Les deux formules décrites ci-dessus peuvent être conclus que l‘utilisation des plus minces cartes de circuit imprimé est bénéfique pour réduire les deux paramètres parasites de vias.

3. L‘alimentation et la broche de terre doivent être percés dans le trou le plus proche. Le plomb entre le trou et la tige doit être aussi courte que possible car ils augmentent l‘inductance. La puissance et câbles de masse doivent être aussi épais que possible pour réduire l‘impédance.

4. Les traces de signal sur le PCB ne devrait pas changer les couches possibles, qui est, essayez de ne pas utiliser vias inutiles.

5. Mettre un peu près de la terre vias vias pour changement de signal pour la boucle la plus proche du signal. Vous pouvez même placer beaucoup de vias au sol supplémentaires sur le circuit imprimé.

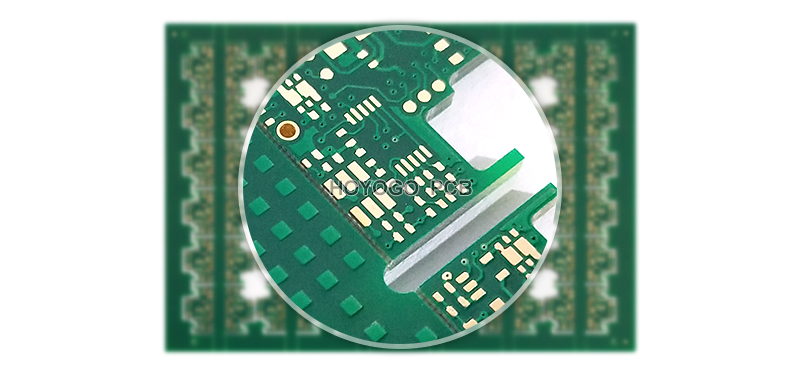

HOYOGO est une organisation internationale, professionnelle,fabricant de PCB fiable. Nous avons 2 bases de production avec une capacité de production mensuelle de 500.000 mètres carrés. Guichet unique offre de produits de PCB et de la solution. Et HOYOGO ont une équipe de direction avec 25 ans d‘expérience dans l‘industrie moyenne et l‘assurance de la qualité fiable.